# SINGLE MAC IMPLEMENTATION OF A 32-COEFFICIENT FIR FILTER USING XILINX

Arpita A. Koli<sup>1</sup>, Nitin Patil<sup>2</sup>

<sup>1,2</sup>Assistant Professor, Dhanajaya Mahadik Group of Institutions, BIMAT, Kagal, (India)

### ABSTRACT

A major trend in the VLSI semiconductor design industry is embedded computing systems, have grown tremendously in recent years. A popular moore's law says that the integration of transistors on a single chip doubles every 18 months, which turns into their complexity. This complexity demands a new type of designer, who can cross the traditional border like complexity, delays, power utilization and to overcome drawbacks of previous designs. Due to advances in VLSI technology, programmable DSP devices are becoming necessary in the signal processing field. To achieve faster signal processing we need separate and faster processors, well known as DSP processors. To achieve implementation of high speed processors, the main processing bottlenecks are the MAC unit, digital filters, which greatly depends on the multiplier, and which greatly depends on the number of multiplication and adder units. In this paper we have proposed an improved time, less complexity design, reduced area of efficient vedic MAC unit and digital FIR filter. So we propose vedic MAC unit, compared with present conventional architectures and its application in designing digital FIR filter of 8 tap and 32 tap filter. The proposed architectures are in Verilog coding, synthesized and simulated using Xilinx ISE 9.1i

#### Index Terms: MAC, Multipliers, adders, FIR filter

#### **I. INTRODUCTION**

Fast execution of algorithms is our essential requirement of a digital signal processing architectures. In order to meet this requirement, DSP architecture must include features that facilitate high speed of operation, less design complexity and large throughputs. In this paper we design a multiplier starting from array, Brown, Wallace and Vedic multipliers of 2x2, 4x4 and 8x8 bits. Adders of RCA and CSA 8x8bits, number of different combination of MAC units using above multipliers and adder units and compare their design relationship. Finally we propose MAC unit application in designing of 8tap and 32tap FIR digital filter. We proposed a MAC unit consisting of adder and accumulator in a same block.

The key component of MAC unit is multiplier that multiplies two n-nit numbers X and Y and gives a product of 2n bits wide, which is added with the contents of the accumulator and saved in the accumulator. Accumulator is acts like a temporary register. Here we have designed MAC units using different combination of multipliers and adders and compare the features mainly speed and area. The speed of the MAC unit is greatly depends on the reduced delay of multiplier. Hence with the suitable choice of the type of the multiplier, the performance of the MAC unit can be made better. Hence we are proposing MAC unit consisting of adder and accumulator in a

## International Journal of Innovative Research in Science and Engineering Vol. No.2, Issue 03, March 2016 www.ijirse.com

same block, by this delay can be decreased and other better performance can be seen in future applications like FIR filter design using MAC unit..

### **II. MAC OPERATION**

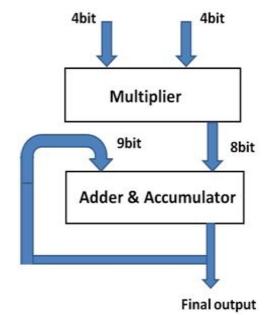

Multiply and accumulate unit mainly used in DSP applications. It consists of mainly multiplier, adder and temporary register as an accumulator. We have designed adder and accumulator in a same block. For this model first apply inputs mxn bits to the multiplier which is being fed from the memory location.

Figure 1: MAC Block diagram

The output of this will be m+n bits which are applied to adder and accumulator unit which is added with the content of the accumulator and save in the accumulator. Primarily the content of accumulator is set to zero, Which is keep on updating with clock cycles, so it is called as temporary register. The final output of accumulator will be m+n+1 bit. The block design is shown in figure in the following sections we design number of different MAC units.

### **III.DIFFERENT MAC UNITS**

#### A. Vedic MAC unit of 4x4bit model

Here we use vedic multipliers of 4x4bit multiplier and simple adder for addition. The vedic multiplication uses 6bit, 4bit CSA while designing a multiplier. Here we can use RCA which is better than CSA.

#### B. Braun 4x4 bit MAC module

Here we use braun multiplier and simple adder for addition. Braun multiplier uses full adders. This multiplier requires 15-multiplications and 12 additions in between adjacent bits.

#### C. Array 4x4 bit MAC module

Here we use array multiplier followed by simple addition operation. This multiplier uses 15 multiplication and addition operations for designing..

# International Journal of Innovative Research in Science and Engineering Vol. No.2, Issue 03, March 2016 www.ijirse.com

#### D. Wallace 4x4 bi MAC Module

This design unit uses Wallace multiplier followed by simple addition. Compare to other multipliers this uses 26 multiplication and 16 addition operations while designing this multiplier.

#### **IV. APPLICATION OF MAC UNIT**

#### Design of digital FIR filter using MAC unit as the main processing unit

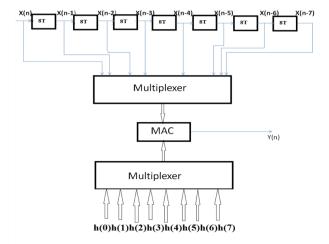

We have proposed 8-tap (8 coefficients) and 32-tap (32 coefficients) FIR filter. The filter can be implemented in many ways depending on the number of multipliers and accumulators available. In this paper we have implemented using a single MAC unit.

There block diagram is shown in fig: which consists of two multiplexers and single MAC unit. The multiplexer is used to select only one input at a time which is fed to the multiplier at a given time. As each product term is generated, it is added to the previously accumulated sum in the MAC unit. Each input sample is delayed from the previous sample by 8T, where T is the time taken by the multiplier and accumulator to compute one product term and add it to the previously accumulated sum in the accumulator.

We are designing a module which implements the FIR equation

i.e  $y(n) = \sum h(i) x(k-i)$

i=0

where k=L+M-1

L= length of x(n) signal

M =length of h(n)

E. Single MAC implementation of an 8-tap FIR filter:

Here we consider x(n) as a 8 samples and h(n) has 8 coefficients, so we used 8:1 mux of two quantities. These multiplexer selects first one sample i.e x(n) and first coefficients h(0) applies to MAC unit. A MAC unit is a single bit MAC unit. The output of this will be saved in accumulator which will be wide bits. In the next clock cycle it selects next sample x(n-1) and next coefficient h(1) and performs MAC operation on these inputs. So this will be apply for all the bits one by one and final output will be y(n) which is saved in accumulator. Here we are using the direct amplitudes of the samples and coefficients

Therefore for above equation  $x(n) - \{11111111\} h(n) = \{11011110\}$

K=8+8-1=15

We start from x(n),x(n-1) = x(n-15) and h(0),h(1) = h(15).

F. Single MAC implementation of an 32-tap FIR filter

Here we consider x(n) as a 32 samples and h(n) has 32 coefficients, so we used 32:1 mux of two quantities. These multiplexer selects first one sample i.e x(n) and first coefficients h(0) applies to MAC unit. A MAC unit is a single bit MAC unit. The output of this will be saved in accumulator which will be wide bits. In the next clock cycle it selects next sample x(n-1) and next coefficient h(1) and performs MAC operation on these inputs. So this will be apply for all the bits one by one and final output will be y(n) which is saved in accumulator. Here we are using the direct amplitudes of the samples and coefficients.

# International Journal of Innovative Research in Science and Engineering

**ISSN: 2454-966**

Vol. No.2, Issue 03, March 2016 www.ijirse.com

K=32+32-1=63

We start from  $x(n),x(n-1)_{--}x(n-63)$  and  $h(0),h(1)_{--}h(63)$ .

### V. RESULTS

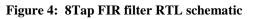

The design is done using Verilog-HDL by using tool Xilinx ISE 10.1i and target family Spartan 3E,Device-XC3S100,speed -5,package: FG320.

| S.No. | MAC Unit    | Logic Delay | Route Deay | Total Delay |  |

|-------|-------------|-------------|------------|-------------|--|

| 1.    | Vedic4x4    | 20.930      | 4.946      | 25.876      |  |

|       | MAC Unit    | 4           |            |             |  |

| 2.    | Braun4x4    | 21.176      | 7.952      | 29.128      |  |

|       | MAC Unit    |             |            |             |  |

| 3.    | Array4x4    | 23.926      | 9.310      | 32.448      |  |

|       | MAC Unit    |             |            |             |  |

| 4.    | Wallace 4x4 | 21.176      | 8.039      | 29.215      |  |

|       | MAC Unit    |             |            |             |  |

TABLE I. Comparison of combinational delay with various 4x4 bit MAC units

| S.No | FIR filter | Logic delay | Route delay | Total delay |  |

|------|------------|-------------|-------------|-------------|--|

| 1.   | 8-Tap      | 3.991ns     | 0.532ns     | 4.522ns     |  |

| 2.   | 32-Tap     | 5.638ns     | 0.532ns     | 6.17ns      |  |

#### **TABLE II:** Comparison of combinational delay

# International Journal of Innovative Research in Science and Engineering

Vol. No.2, Issue 03, March 2016 www.ijirse.com

| 🖾 XII no Ni MyrojestVir_Bilis_D.inc - (Simulation)                                                                                                                                                          |                         |                    |           |                         |        |                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------|-----------|-------------------------|--------|-----------------|

| 😧 Hin Edit Hen Project Source Process TestBench Simulation Wedon Help                                                                                                                                       | L. 8. 8                 |                    |           |                         |        |                 |

| D 👌 🗑 🖉 👌 😹 5 0 X N M 🛛 🖉 🖉 P X X A S S S D D P V M S • 💿 V ք Ø S S S S S S O O                                                                                                                             |                         |                    |           |                         |        |                 |

| (+) □□□□ A 35 35 (由本) 1 合产性 ■ 1 年 ▶ ▶ ▶ 1000 ● ● ●                                                                                                                                                          |                         |                    |           |                         |        |                 |

|                                                                                                                                                                                                             |                         | 520)<br>x70)<br>CK | s(20)<br> | dk<br>reset<br>y1<br>y2 | z(310) | <u>z(\$1:0)</u> |

|                                                                                                                                                                                                             | 3                       | reset              |           |                         |        |                 |

| Tennes to fair forme in this function preserve.<br>Printed struct annual former in this function preserve.<br>Printed struct introduction preserve.<br>Comm & Otom & Avenue & Total & Avenue & Docume ALLee | *                       | <u>N(2:0)</u>      |           |                         |        |                 |

|                                                                                                                                                                                                             | Tite -                  |                    |           |                         |        |                 |

|                                                                                                                                                                                                             |                         |                    |           |                         |        |                 |

| 🚺 start 🔰 🖄 Max (12 - Lipepe). 📓 Decent (-Normal). 🎽 united - Fert                                                                                                                                          | () 建筑 0, (0, 1) + 12.44 |                    |           |                         |        |                 |

|                                                                                                                                                                                                             |                         |                    |           |                         |        |                 |

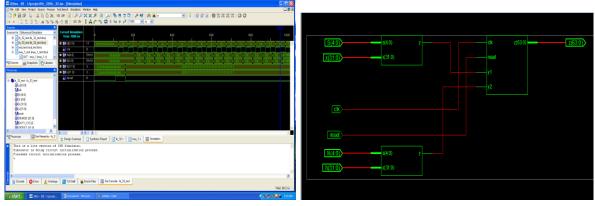

Figure 3: 8Tap FiR filter simulation Result

Figure: 5 32Tap FIR filter Simulation Results Figure 6: 32 Tap FII

Figure 6: 32 Tap FIR filter RTL schematic

#### VI. CONCLUSION

In this paper we have approached new concept of designing single MAC unit based finite impulse response filter using FPGA. We have designed 8 and 32 coefficients FIR filter successfully with reduced latency. We have used fastest MAC unit for designing FIR filter, thus yielding high speed. The figures show the simulation results with reduced latency.

#### REFERENCES

- Ashish B. Kharate, Prof. P.R. Gumble" VLSI Design and Implementation of Low Power MAC for Digital FIR Filter" 2013

- [2] Shrikant Patel" DESIGN AND IMPLEMENTATION OF 31-ORDER FIR LOW-PASS FILTER USINGMODIFIED DISTRIBUTED ARITHMETICBASED ON FPGA" 2013Volume 2 - Issue 2 April 2014

- [3] Sachin B. Jadhav, Nikhil N. Mane" A Novel High Speed FPGA Architecture for FIR Filter Design" 2012

- [4] K. Neelima, M. Bharathi" An Algorithm for FPGA based Implementation of Variable Precision MAC unit for High Performance Digital FIR Filters" 2012

- [5] M.Lakshmanna, N.Praveenkumar, M.Tech(Ph.D), G.Harikumar" FPGA implementation of High Order FIR Filter Using Distributed Arithmetic operation"

### International Journal of Innovative Research in Science and Engineering Vol. No.2, Issue 03, March 2016 www.ijirse.com

- [6] J.Ravi, K. Rama Rao, N. Tirumala" Design of Efficient FIR Filter MAC unit UsingParallel Prefix Adder"2014

- [7] N. Jhansi, B.R.B Jaswanth" Design and Analysis of High Performance FIR Filter using MAC Unit"2014

- [8] Shraddha S. Borkar , Awani S. Khobragade" Optimization of FIR digital filter using low power MAC"

- [9] Anna Johnson, Binu Manohar, Anu Philip Mathew" Modified MAC based FIR Filter Using Carry Select Adders"2015

- [10] SWETA KUMARI, SANGITA KUMARI, MANSI WAGHELA" VLSI DESIGN AND IMPLEMENTATION OF FIR DIGITAL FILTER USING LOW POWER MAC"2014.